輝達新核彈,站在蘋果的肩膀上

2024GTC大會上,黃仁勳右手B200,左手H100,理所當然地有了新人忘舊人:「我們需要更大的GPU,如果不能更大,就把更多GPU組合在一起,變成更大的虛擬GPU。 」

輝達公佈的Blackwell架構的B200 GPU,親手把網紅顯示卡H100拍在了沙灘上。

依照黃仁勳的介紹,B200理論上的AI性能可達20PFLOPS,是H100的五倍。相較於H100的800億電晶體規模,B200的電晶體規模高達2080億。

一般來說,晶片算力提升的最常用方法是採用先進製程,用更高的密度在晶片裡塞進更多電晶體。如摩爾定律所說:

在積體電路上可以容納的電晶體數目,大約每經過18個月到24個月就會增加一倍。

例如採用7nm製程的A100 GPU,晶片(Die)面積為826mm ²,內有542億電晶體;採用5nm(台積電N4)製程的H100,晶片面積縮小為814mm ²,電晶體數量反而暴漲至800億。

然而,B200在電晶體數量提高近三倍的同時,並沒有用更先進的3nm工藝,而是採用了和H100一樣的5nm工藝。黃仁勳所說的“大”和“組合”,是字面上的:

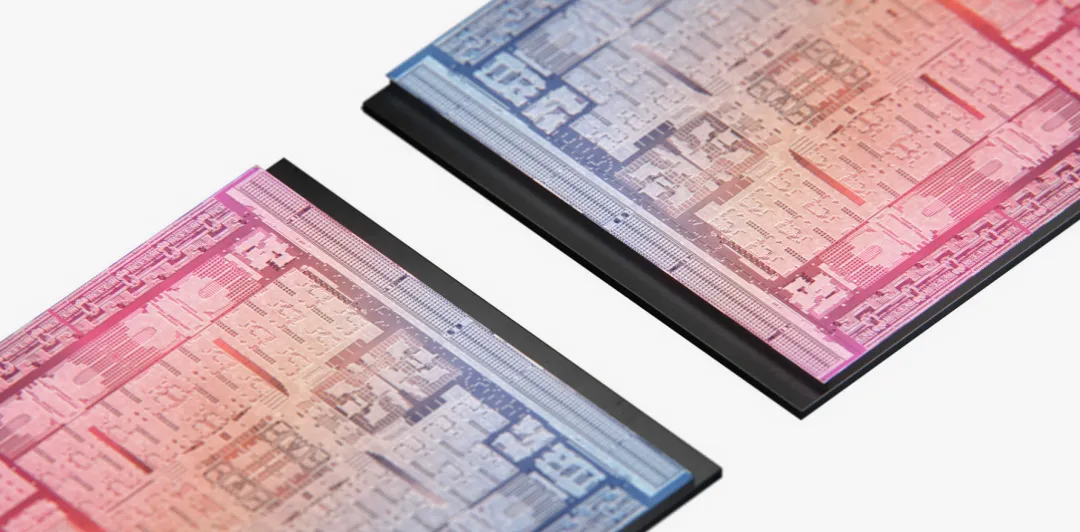

從技術原理來看,B200其實是把兩塊晶片「拼」成了一個大晶片。

在輝達的PPT展示裡,兩顆GPU從邊緣「無縫黏合」在一起,面積X2的同時,算力翻倍。

1+1有時不等於2

工廠提高生產力有兩種方法:一是擴建廠房,裝進更多的生產線;二是升級生產線,在廠房面積不變的情況下,增加生產線數量。

晶片公司一直以來都在採用第二種方法:透過生產線創新(製程流程),在有限的晶片面積裡塞進更多晶體管,避免擴建廠房帶來的房租成本上漲。

但這種方式的限制在於,生產線創新(製程)對應的研發成本越來越高,甚至有高過房租的趨勢。 H100採用的5nm工藝,很可能就是GPU量產的極限製程,繼續下探到3nm,很可能成本上吃虧。

擴建廠房的確是一個辦法,但放在晶片生產上,會遇到一個中國人很熟悉的問題:土地供應有限。

每一顆晶片都是從12吋的矽晶圓(土地)上「切」下來的,那麼晶片(廠房)面積越大,每塊晶圓能「切」出來的晶片就越少。

再考慮到良率和大面積晶片的散熱問題(施工事故),單一晶片成本會倍增。

由此衍生出了第三種想法:建造一個一模一樣的廠房,讓兩個廠房同時生產,既避開了成本問題,又提高了生產效率。

這種方法聽起來簡單,但實踐起來難於登天。

晶片在執行計算任務時需要經歷兩個階段:數據傳輸和計算,數據傳輸花費時間過多,計算“空載”,就會造成算力的浪費。就像兩間廠房需要一個工頭傳達指示,工頭在A廠房發表演說時,B廠房的工人都在摸魚。

這就導致在一塊主機板上封裝10顆晶片,效能不但不會提高10倍,反而很可能連兩倍都不到。

2011年,輝達發表了GTX590顯示卡,最大特色是在一個PCB板上裝了兩顆GPU晶片。

但在具體的遊戲中,想同時調用兩顆GPU的算力,不僅需要專門的軟體支持,性能也只有單顆晶片的130%左右。

原因就在於,大量的算力被低效率的資料傳輸浪費了。

為了解決產線工人趁著工頭不在消極怠工的問題,輝達團隊在2017年發表論文,提出了名為「可組合封裝GPU」的架構,核心在於將多顆GPU整合在同一個晶片封裝內。

傳統的晶片封裝是“先封再拼”,即兩顆晶片封裝完畢,再用導線連接。輝達的方案是“先拼再封”,先把兩顆晶片拼成一個大晶片,再封裝到一起。

把晶片(廠房)之間的物理距離縮減到0,工頭傳遞指示,兩邊的工人同時學習貫徹,降低資料傳輸時間,實現1+1=2。

幾個月後,老對手AMD表示論文誰不會寫,刊發論文展示了4顆GPU集成在同一封裝內的設計,宣稱其性能比當時的最強GPU還要高45.5%,並且coming soon。

但無論是輝達還是AMD,都沒能把這個方案真正「soon」出來。

第一個讓1+1=2的,是蘋果。

蘋果的超能力就是有錢

2022年,蘋果發布了M1 Ultra晶片,其最大特點是直接將兩顆M1 Max晶片「黏合」在一起,變成一張大晶片,業內戲稱「膠水大法」。

1+1=2的意義正如蘋果在新聞稿中所說:

M1 Ultra 在工作時依然表現出一枚晶片的整體性,也會被所有軟體識別為一枚完整晶片,開發者無需重寫程式碼就能直接運用它的強大效能。這在史上從無先例。

蘋果之前,幾乎所有的「縫合」方案,都無法解決晶片在連接過程中產生的損耗,使得效能往往「1+1<2」。 M1 Ultra的背後,是一個名為UltraFusion的「縫合技術」。

根據蘋果官方的說法,Ultra Fusion由蘋果與台積電共同研發。但從經驗來看,蘋果發揮的最大作用,是以「技術冠名費」的方式,報銷了台積電的研發開支。

兩顆晶片的縫合,核心是要解決晶片間的資料傳輸問題。

為了實現“無縫粘合”,蘋果用上了台積電最昂貴、最先進的封裝技術——第五代CoWoS-S。 [2]

傳統的傳輸方式是將兩顆晶片封裝在一塊基板上,晶片之間的傳輸由引線解決。 CoWoS方案在基板和晶片之間加了一層矽中介層,透過在矽中介層佈線,間接將兩顆小晶片連接起來,連接密度是現有技術的兩倍。

這個技術的關鍵就在於矽中介層,也是燒錢的根源。

矽中階層本質上是一片矽晶圓,也就是「切」晶片的原料。光是為了做連接,就要另加一層矽晶圓的費用,這手筆恐怕只有蘋果做得出來。

後來,輝達在H100上採用了更成熟的CoWoS,成本仍超過4000美元。蘋果作為最初的試誤者,成本只會更高。

除了CoWoS,蘋果的錢還燒在了「縫合」技術上[2]。

晶片製造的本質,是在矽晶圓上刻畫複雜電路。但在實際製造過程中,電路不是直接刻在矽晶圓上的,而是先刻在一個掩膜版上,再透過光刻和蝕刻電路「轉移」到矽晶圓上。

輝達當年遇到的問題是,GPU晶片本身面積就大,一旦兩顆GPU拼接,就會超過正常遮罩版的大小(H100的面積已經接近台積電5nm遮罩版的極限),電路就無法被完整地刻畫。

蘋果提出的解決方案是,1個掩膜版不夠,咱直接上四個吧。

透過四個遮罩版“縫合”,將電路刻畫的面積增加到2500mm ²,是輝達同期GPU的3倍多(815mm ²)。

在晶片製造中,很大一部分成本就來自於掩膜版製作。

掩膜版生產需要Mask Writer(掩膜版寫入機),精密程度堪比光刻機。而且Mask Writer只在遮罩版製作時使用,每種晶片只做一次,難以稀釋成本。

除此之外,由於Ultra Fusion用到了大量新技術,例如連接晶片的高縱橫比矽通孔(TSV)技術,用於散熱的新型非凝膠型熱界面材料(TIM)等[2],台積電都是拿著發票找蘋果報銷的。

M1 Ultra發佈時,業界都沒有準確的成本推算。不是研究員水平不到位,實在是技術太先進,算不出來。

高科技產業最關鍵的問題不是技術如何實現,而是誰來掏錢把論文和實驗室裡的數據變成可以量產的產品。不知道看著M1 Ultra的拼接示意圖,會不會有久遠的記憶攻擊黃仁勳。

科技狂人的商業冒險

最早試圖解決的1+1<2問題的,既不是輝達也不是蘋果,而是台積電元老蔣尚義。

2009年,回歸台積電的張忠謀請回已經退休的蔣尚義。在後者帶領下,台積電以「後閘級」技術路線成功超越三星率先量產28nm製程。但在研發過程中,蔣尚義發現電晶體單位製造成本不降反升,製程升級提升效能的性價比開始降低。

拿著張忠謀批的1億美元預算和400多人的工程師團隊,蔣尚義帶隊開始了「超越摩爾計畫」。

傳統互聯技術下,傳輸速率已經觸及天花板。蔣尚義開始嘗試一種新思路:

把兩顆晶片放到一起封裝,物理距離縮短了,傳輸速度自然提高。為了區別於傳統封裝,蔣尚義將其命名為「先進封裝」。

2011年,台積電得到FPGA大廠賽靈思訂單,憑藉CoWoS以及共同開發的矽通孔(TSV)等技術,成功將4個28nm FPGA晶片拼接在一起,推出了史上最大的FPGA晶片。

然而,大部分客戶對CoWoS興致寥寥,賽靈思的訂單杯水車薪。

不是台積電技術不夠好,實在是先進封裝太貴了。

老客戶高通的高管在與蔣尚義共進午餐時直白表示,CoWoS技術很好,但“我只願意為它花費1美分/平方毫米”,而台積電當時的售價是7美分/平方毫米[3]。

據說輝達也是台積電CoWoS的第一批目標客戶之一,因為資料傳輸的瓶頸一直是困擾GPU運算的核心問題。但聽到台積電的報價後,輝達當場表示,老技術還能再湊合幾年[3]。

另一方面,先進過程還在穩步推進,先進封裝的概念顯得過於超前,畢竟領導還在開卡羅拉,你就別急著換寶馬了。

因此,先進封裝團隊在台積電內部的一度邊緣化,甚至被當作老幹部療養院。後來跳槽三星的梁孟松,就認為自己被調往先進封裝業務屬於「下放」。

隨後,台積電開始給CoWoS做減法,掏出了替代方案“ InFO ”,將昂貴的矽中介層換成其他材料,犧牲了連接密度,但成本大幅下降。

緊接著,台積電遇到了可以靠一己之力改變供應商命運的超級甲方:蘋果。

2013年前後,由於與三星在手機市場的競爭,蘋果開始將晶片代工交由台積電。

憑藉InFO方案,台積電在16nm製程的基礎上,製造出了比三星14nm性能更強的A10處理器,貢獻了歷代iPhone中第二輕薄的iPhone 7[5]。

有了蘋果的大單的,台積電的先進封裝業務迅速盤活,並在2022年拿出了震驚業界的M1 Ultra晶片。 2024年開年,這個攻堅十多年的“膠水大法”,又被用在了輝達的新核彈B200上。輝達順勢拿下冠名權,將這項技術命名為「NV-HBI」。

先進封裝方案依然昂貴,但對今天的輝達來說,成本兩個字怎麼寫,他們可能已經忘了。

尾聲

除了CoWoS,另一個被生成式AI帶火的技術HBM,其探索同樣可以追溯到十年前

CoWoS拿到賽靈思的第一筆訂單時,蔣尚義大喜過望,但賽靈思的動機卻讓他有些哭笑不得:把四個老晶片拼在一起,直接當成新產品加價賣,就不用自己開發新產品了[3]。

在美國電腦歷史博物館的訪談中,蔣尚義回憶 [3]:「我開發技術的初衷是解決效能瓶頸問題,在我看來,我的創新並沒有被用在好的地方」。

科技革命很難推動技術創新,反而是技術創新讓科技革命成為可能。創造歷史的人,永遠無法預見自己在歷史進程中的座標。

在我們不曾踏足的物理學的邊境,還有無數偉大的創新尚在不為人知的角落。(遠川科技評論)