鑽石晶片,首次實現

鑽石(diamond,也譯作鑽石)在所有用於下一代電子設備的已知半導體中擁有最高的品質因數(figure-of-merits ),表現遠遠超出了傳統半導體矽的性能。為了實現鑽石積體電路,我們需要開發具有n 通道和p 通道導電性的鑽石互補金屬氧化物半導體(CMOS) 元件,就像為半導體矽建立的元件一樣。

然而,由於n 型通道MOS 場效電晶體(MOSFET) 的挑戰,鑽石CMOS 從未實現。在這裡,我們基於step-flow nucleation 模式製造了具有原子級平坦表面的電子級磷摻雜(phosphorus-doped)n型鑽石外延層。因此,展示了n 通道鑽石MOSFET。 n型鑽石MOSFET在573 K時表現出約150 cm 2 V -1 s -1的高場效應遷移率,這是所有基於寬帶隙半導體的n溝道MOSFET中最高的。

這項工作有助於開發節能且高可靠性的CMOS 積體電路,用於惡劣環境下的高功率電子元件、整合式自旋電子學和極端感測器。

簡介

現代電子學以矽互補金屬氧化物半導體(CMOS) 技術為主導。然而,矽CMOS一直面臨高功率密度、高頻、高溫、高輻射等條件的瓶頸。

與其他半導體相比,鑽石因其優越的特性而被視為終極半導體。鑽石CMOS 元件長期以來致力於實現超越傳統矽電子元件能力的效能。透過使用鑽石電子元件,不僅可以減輕傳統半導體的熱管理需求,而且這些設備的能源效率更高,並且可以承受更高的擊穿電壓和惡劣的環境。

另一方面,隨著鑽石生長技術、電力電子學、自旋電子學、和可在高溫和強輻射條件下工作的微機電系統(MEMS)感測器的發展,基於鑽石CMOS元件的外圍電路需求已增加了單晶片集成度。 P型鑽石很容易透過大量硼摻雜或氫封端鑽石表面的表面轉移摻雜來獲得。 (P-type diamonds are readily accessible through bulk boron doping or surface transfer doping of a hydrogen-terminated diamond surface.)然而,為了實現鑽石CMOS,必須實現對稱摻雜控制,就像半導體矽所實現的那樣。因此,需要開發鑽石n-MOS。

然而,由於電子級高品質n型鑽石生長面臨重大挑戰,n溝道鑽石MOSFET長期以來一直是個障礙,至今尚未實現。

迄今為止,磷(phosphorus)已被認為是室溫下唯一可靠的最淺n 型摻雜劑,儘管與C (0.77 Å) 相比,P (1.08 Å) 的共價半徑(covalent radius )較大且平衡形成能較高(high equilibrium formation energy ) (4–5.7 eV) )。然而,由於磷摻雜鑽石中載子補償比較大,在約1017cm-3的低施主濃度下(low donor concentration)很難實現n型導電,阻礙了n溝道MOSFET的發展。除了磷半徑比碳大而造成的缺陷之外,化學氣相沉積(CVD) 過程中將大量氫摻入鑽石外延層也會鈍化磷原子並降低電導率。

在這項研究中,基於階梯流橫向生長模式(step-flow lateral growth mode)實現了具有原子級平坦平台的電子級n型鑽石。因此,在不觀察跳躍電導率的情況下獲得了具有約10 17 cm -3的低施主濃度的N型鑽石。因此,可在573 K 工作溫度的n 型鑽石MOSFET 已成功開發。 573 K下的實驗場效應電子遷移率約為150cm 2 V -1 s -1,是高溫下所有寬帶隙半導體中最高的。

結果與討論

高品質摻磷鑽石外延層

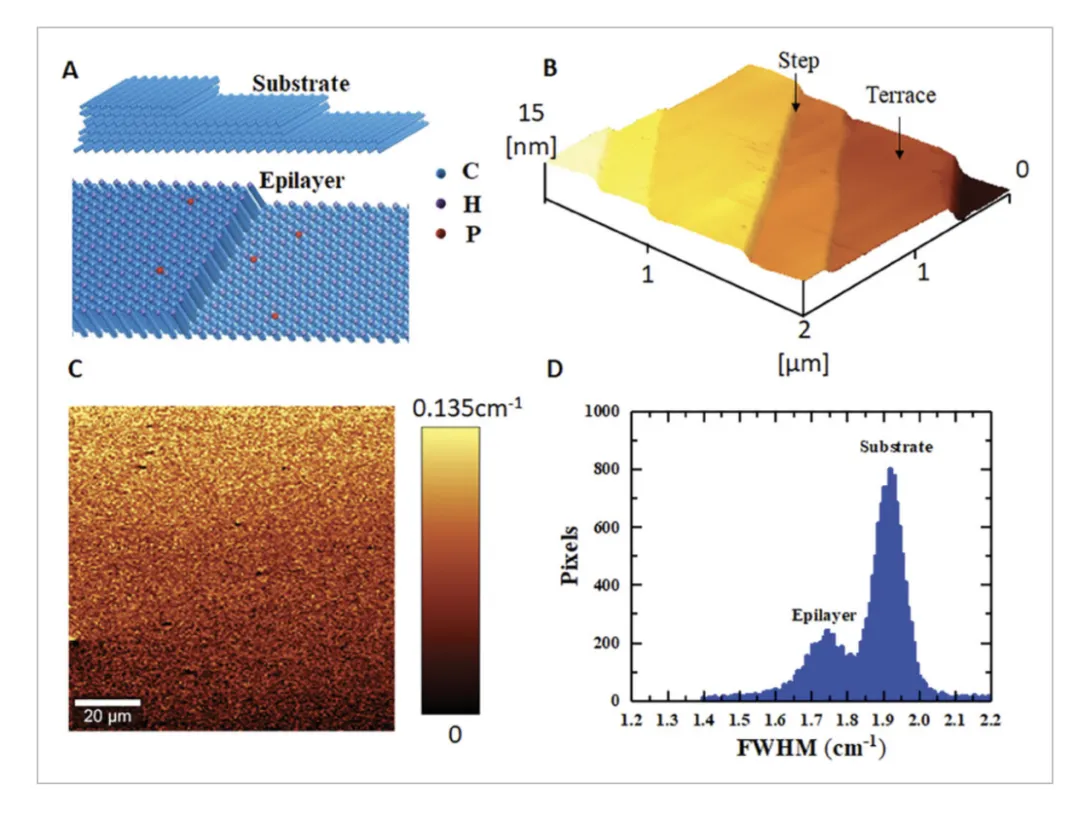

我們透過微波等離子體化學氣相沉積(MPCVD:microwave plasma chemical vapor deposition) 在Ib (111) 型取向高壓高溫(HPHT:high-pressure high-temperature) 鑽石基板上生長了磷摻雜鑽石外延層。 n型鑽石包含兩個磷摻雜外延層:用於元件通道的輕摻雜(lightly doped)n-鑽石外延層和歐姆接觸的重磷摻雜鑽石外延層。

600 nm 厚的輕摻雜n-層鑽石外延層直接生長在HPHT 鑽石基板上。隨後,利用自製的MPCVD反應器在n-層上沉積了100 nm厚的重磷摻雜n+層,並提高了磷摻入鑽石外延層的效率。生長的鑽石(111) 具有未重構的一氫化物封端表面(unreconstructed monohydride-terminated surface)。 n-型鑽石在鑽石(111)基板上的同質外延生長遵循階梯流生長模式。

透過原子力顯微鏡(AFM:atomic force microscopy)觀察,形成了原子級平坦的平台(圖1A),如圖1B所示;圖S1(支援資訊),平均粗糙度(Ra) ≈0.1 nm。儘管在整個外延層中形成了台階,但對於10 × 10 µm 2的較大區域,平台的平均粗糙度為˂ 1 nm (圖S2 ,支援資訊)。平台寬度(terrace width)為數百奈米,台階高度(step height)約為3奈米(圖S3,支援資訊)。表面台階(surface steps )是由HPHT 鑽石(111) 基材的誤切所造成的。

由此可見,階梯流生長模式產生了高品質的n-鑽石外延層。拉曼圖(Raman mapping)顯示鑽石的特徵峰在0.135 cm -1範圍內表現出較小的色散,並且n-鑽石外延層的鑽石峰的半高全寬(FWHM:full-width at the half maximum)集中在1.75 cm -1處,優於HPHT 鑽石基材的1.95 cm -1(圖1C、D)。

n-層中的應力低至-12 MPa ,晶體質量與在(100)鑽石基板上生長的同質外延鑽石層相當。如果假設壓應力主要是由磷原子的摻入引起的,則CVD 鑽石外延層中磷濃度的橫向分佈是均勻的。 n + /n −的磷濃度使用二次離子質譜(SIMS:secondary ion mass spectrometry) 測量鑽石基底上的鑽石,如圖S4(支持資訊)所示。 100nm厚的n +層的磷濃度約為10 20 cm -3。 600nm厚的輕摻雜n -層鑽石外延層的磷濃度為ND ≈10 17 cm -3。 SIMS 數據中可以觀察到磷濃度沿著生長方向均勻分佈。

另外,SIMS深度剖面顯示氫含量被控制在10 17 cm -3的噪音水準。磷和氫原子良好控制地摻入鑽石外延層意味著鑽石外延層具有高晶體質量,這對於實現n 型導電性至關重要。此外,沒有從外延層檢測到與氮空位(nitrogen-vacancy)相關的發光。

由於鑽石中磷的深層性質,電子濃度很大程度取決於溫度。電子濃度計算如下:

其中n表示導帶中的自由電子濃度,N D表示磷濃度(phosphorous concentration),N A表示補償受主密度(compensating acceptor density),N C表示有效導帶態密度(effective conduction band density of states) ,g表示施主簡併因子(degeneration factor of the donors),E D表示供體的活化能(the activation energy of the donors),k B是玻爾茲曼常數,T表示溫度。

電子密度在300 K 時約為10 10 cm -3,在573 K 時增加了四個數量級,N D約為10 17 cm -3(圖S5,支持資訊)。補償受主濃度N A約為2×10 16 cm -3。在室溫下,經由霍爾效應測得的電子遷移率約為623cm 2 V -1 s -1。輕摻雜的n -層即使在573 K 時也表現出212cm 2 V -1 s -1的高電子遷移率(圖S6,支援資訊)。輕摻雜n -層薄膜的電阻率在室溫下約為10 6 Ω cm,在573 K時降至100Ω cm(圖S7,支持資訊),熱活化能E D約為0.57 eV。

N型鑽石MOSFET的電氣特性

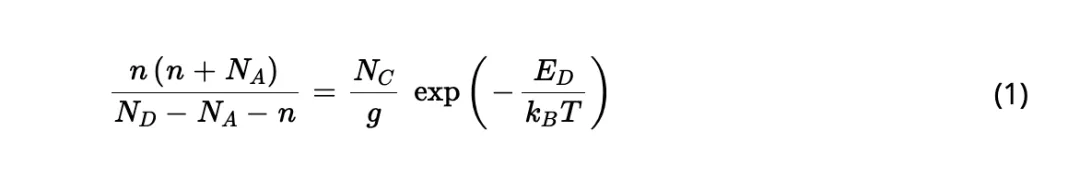

我們製造了具有兩種幾何形狀的n 通道鑽石MOSFET:rectangular 和Corbino(圖2;表S1,支援資訊)。源極(S)和汲極(D)接觸形成在重磷摻雜的n+層上,該層是退火(annealed)的Ti(50 nm)/Pt(10 nm)/Au(60 nm)。重摻雜n +鑽石的電阻率在室溫下約為80 Ω cm,在573 K 時為20 Ω cm。輕摻雜磷n -層用作MOSFET 的通道。 S 和D 電極之間的頂部重摻雜n +鑽石層在氧等離子體中蝕刻,直到到達輕摻雜層。

閘極氧化物是在473 K 下經由原子層沉積(ALD) 沉積的30 nm 厚的Al 2 O 3。柵極金屬由10 nm 厚的Ti 層和60 nm 厚的Au 層覆蓋組成。閘極長度( L g )為5μm和10μm,源極-汲極( L sg )和汲極-閘極間隔( L dg )分別為5μm和10μm。

Corbino MOSFET 閘極的內徑和外徑分別為220 µm 和230 µm。對於此處研究的rectangular MOSFET(1 號元件),L g為5 µm,L sg = L dg = 10 µm,閘極寬度約900 µm。圖2A、B分別顯示了n 型鑽石MOSFET 的原理圖和光學影像。 MOSFET 的電氣特性是在真空室(10 -3 Pa) 中使用半導體參數分析儀和屏蔽探針台進行的。為了進行電氣特性表徵,MOSFET 的溫度從室溫升至573 K。

圖2C顯示了矩形MOSFET 的汲極電流( I d )(透過閘極寬度歸一化)與汲極電壓( V ds )的關係。在這裡,我們展示了在三個溫度下測量的I d – V ds特性:300 K (RT)、423 K (150 °C) 和573 K (300 °C)。 MOSFET 的閘極電壓( V gs ) 在-20 至10 V 之間變化,步長(steps)為5 V。漏極電流由閘極電壓很好地調製,顯示出典型的n 型通道電晶體行為。 V ds = 20 和V gs = 5 V 時的最大漏極電流( I d,sat )在300 K 時約為0.027 µA mm -1。然而,進一步增加V gs > 5 V 導致漏極電流幾乎沒有改善,因為到高串聯電阻。直到MOSFET 的汲極電流在某個溫度下隨時間穩定為止,獲得與溫度相關的I d − V ds特性。

如圖2C(ii)、(iii)所示,由於磷的熱電離,漏極電流隨著溫度的升高而顯著增加。在高溫下且V ds = 20 V 和V gs = 10 V 時,漏極電流在423 K 時增加至2.9 µA mm -1,在573 K 時增加至10 5 µA mm -1,分別比該值高出兩個和四個數量級分別為300 K。這與電阻率對溫度的依賴性一致(圖S7,支援資訊)。達到飽和所需的汲極電壓隨著溫度和閘極電壓的增加而增加,在573 K 和V gs = 10 V時飽和時,V ds > 30 V。估計導通電阻在RT 時約為5 GΩ mm ,在573 K、 V gs = 10 V時會減少至160 kΩ mm。其他溫度下MOSFET 電氣特性的變化如圖S8 – S12(支援資訊)所示。不同閘極電壓下汲極電流對測量溫度的依賴性(圖S13,支援資訊)。漏極電流隨溫度呈指數增加。使用溫度相關漏極電流的阿倫尼烏斯方程式進行擬合可提供0.45 eV 的熱活化能。

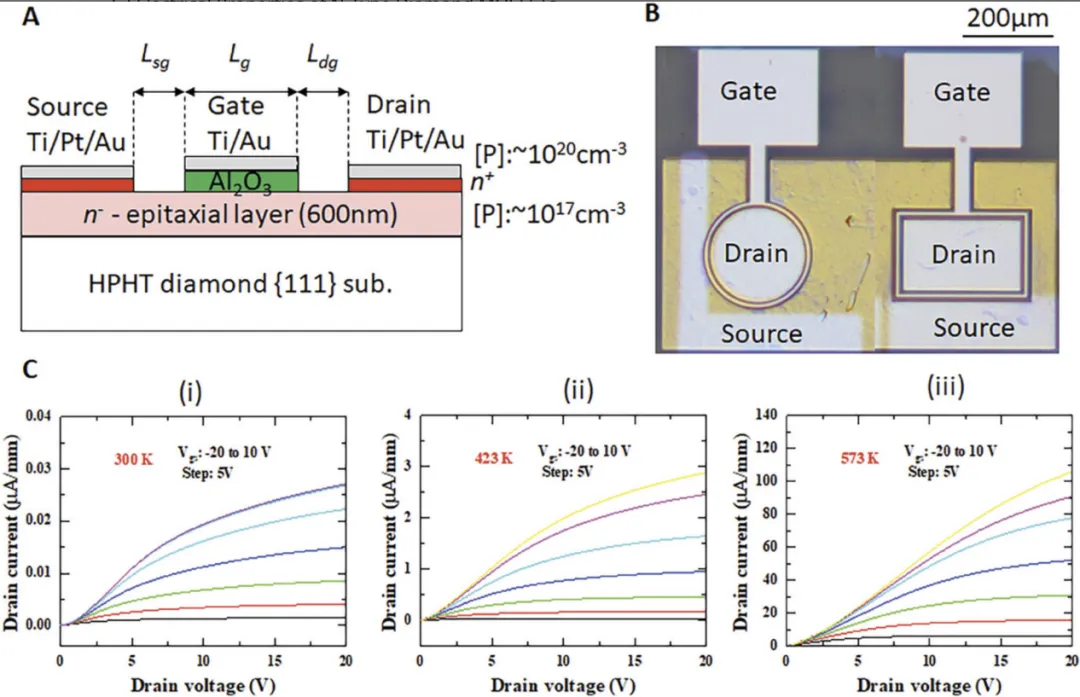

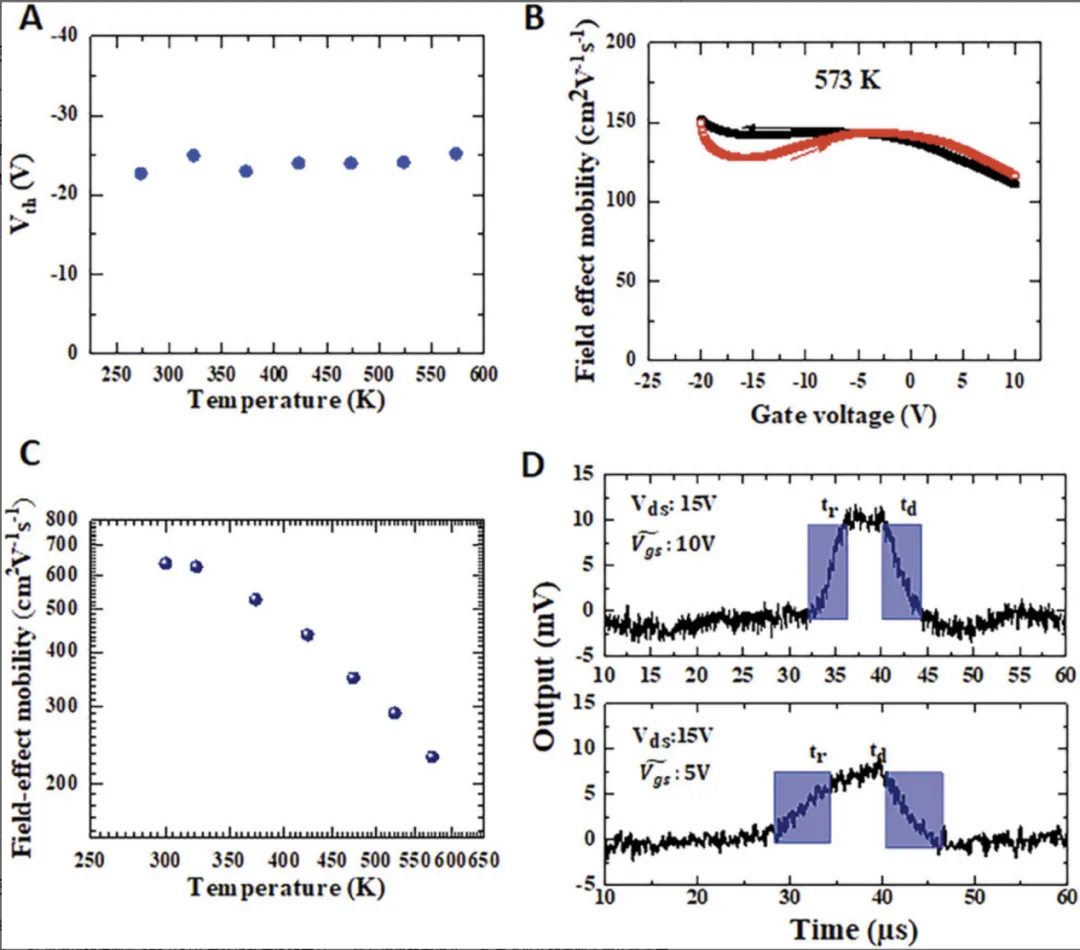

MOSFET 的傳輸特性或與閘極電壓相關的汲極電流如圖3A ( 300 K 時)及圖3C(573 K(573 K)、 飽和區V ds = 20 V 時)。在V ds = 20 V 時,閘極電壓為10 V 和−20 V 時的汲極電流比在RT 下> 200,在573 K 下為100 倍。與基於硼摻雜鑽石的MOSFET 類似,n 型鑽石MOSFET 表現出深度耗盡模式。在低於473 K 的溫度下,在傳輸曲線中觀察到很小的滯後。在573 K 時僅觀察到輕微的滯後。最大跨導g m在300 K 時約為0.012 µS mm -1,在573 K 時約為4 µS mm -1。使用V gs與I d 0.5的圖形方法提取閾值電壓( V th ) (圖3B,D ),即≈−25 V。 V th隨閘極掃描方向、閘極掃描方向或溫度的變化很小(圖4A)。也測量了具有不同幾何形狀的其他裝置,其電氣特性如圖S14 – S17 (支援資訊)所示,並且觀察到了類似的n 通道行為。例如最大飽和漏極電流、最大跨導、閾值電壓和溫度等電氣性能,與具有相似尺寸的MOSFET 相當(表S1,支援資訊)。

場效應電子遷移率建模

對於遷移率不依賴閘極電壓或串聯電阻的理想MOSFET,可以使用飽和區的二次模型計算有效電子遷移率µ eff,如下所示:

其中I d,stat表示飽和區的漏極電流,C ox表示閘極氧化物的電容。我們嘗試使用方程式( 2 )來確定場效應電子遷移率。然而,在300 K時,場效應遷移率低至0.02cm 2 V -1 s -1,明顯偏離霍爾測量所測得的合理值(低近3000倍)。將串聯電阻代入等式(2)不會導致遷移率本質上改變。隨著溫度的升高,觀察到場效應電子遷移率增加,這是不合理的。在573 K時,使用公式( 2 )計算出的電子遷移率約為150 cm 2 V -1 s -1(圖4B),在高溫下遠高於基於SiC、GaN和Ga 2 O 3的n溝道MOSFET 。請注意,由於源極/汲極和漂移區中的大串聯電阻以及鑽石中磷的部分熱電離,即使在573 K 時遷移率也被低估。

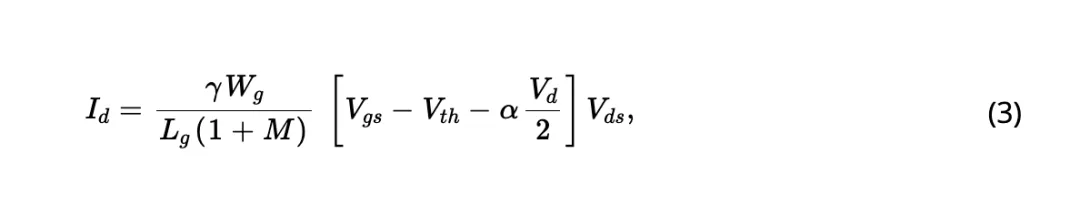

為了精確評估場效應遷移率,我們考慮i) 磷供體的熱電離效率,ii) 串聯電阻,以及iii) 遷移率降低因素(即缺陷散射)。因此,在線性區,漏極電流(I d)可表示為:

其中M表示施主佔據因子(donor occupancy factor),即束縛施主電荷與通道電荷的比率(a ratio of bound donor charge to channel charge),反映施主的電離率(ionization rate of the donor ),並與電子的準費米能階(the quasi Femi level of electrons)相關。

在這裡,我們假設M 與通道深度無關。請注意,M 的解析形式與自由電子密度與摻雜密度之比不同(支援資訊)。 M越大,自由電子密度與摻雜密度的比值越小。 α 是與施主濃度相關的降低漏極電流的因子,此處約為1.1。 γ 包括調節遷移率的θ 和η 因子(支持資訊)。因子θ與常規載子散射和串聯電阻的影響有關。漏極電壓對載子遷移率的影響與γ所包含的參數η有關。非零的η 主要是由於氧蝕刻導致奈米級/微米級檯面結構的不規則性。在遠高於閾值電壓的區域中模擬電子遷移率。由於汲極電壓小、源汲極距離大、閘極長度大,不考慮載子速度的飽和。

模擬中鑽石中磷的熱電離設定為0.57 eV。我們得到了n型MOSFET在0V閘極電壓下的場效應遷移率,如圖4C所示。在300 K 時遷移率模擬為約638 cm 2 V -1 s -1,考慮施主佔據因子M 和串聯電阻,遷移率在573 K 時降低至約200 cm 2 V -1 s -1。對於理想的MOSFET,M 隨著電流的增加而減少,最終達到零。 M 在300 K 時計算為2278,在573 K 時降至≈4(圖S18,支援資訊),揭示了n 型鑽石MOSFET 耗盡模式。值得注意的是,沒有考慮補償受體效應。透過考慮施主佔用因子和串聯電阻,漏極電壓與汲極電流的類比特性顯示在SM 中(圖S19 ,支援資訊)。低漏極電壓區域有輕微差異,主要是由於S 和D 電極中n +和n -層之間的勢壘所致。

我們注意到,模擬是在假設整個n -層導電的情況下進行的。考慮到氧封端磷摻雜(oxygen-terminated phosphorous-doped)n型(111)鑽石的Femi能階pining,會發生溝道的次表面耗盡(depletion)。使用類似的n-金屬肖特基FET 進行模擬-通道鑽石層顯示亞耗盡層約為50 nm。對於n 型MOSFET,沿著絕緣體中固定電荷的Femi 能階pining會修改模擬中的Femi 電位。應進行詳細的實驗和理論研究,以揭示未來缺陷狀態的影響。

目前,p溝道鑽石MOSFET已廣泛開發,並已建立常規製造流程。由於缺乏鑽石n-MOS,據報道使用鑽石p-MOS 和III 族氮化物n-MOS 可以實現互補電路。雖然這是一個很有前途的策略,但全鑽石CMOS是充分利用鑽石品質因數的終極追求,特別是對於在惡劣環境(高溫和強輻射)下運行的電子產品。對於高頻工作,與截止頻率超過GHz的H端電晶體相比, n型鑽石MOSFET的串聯電阻仍然很大,在室溫下超過10 9 Ω mm -1。因此,運行速度被限制在千赫茲範圍內。然而,在溫度> 573 K 時,串聯電阻會降低三個數量級以上。開關速度為˂ 5 µs(圖4D),也可以透過施加在閘極的訊號來調節。

由於通道電導率的增加,閘極振幅越大,開關速度越快。透過優化裝置幾何形狀,例如減少漂移區空間和閘極長度,工作頻率可以超過兆赫茲範圍,輕鬆滿足輻射偵測器和MEMS感測器的混合訊號電路的要求。此外,n型鑽石可以穩定帶負電的氮空位(NV -)態,大大提高靈敏度。因此,鑽石CMOS 整合NV 中心有利於鑽石自旋電子元件的開發,這些元件需要專門的可控性和完整性來擴展量子感測協定。

鑽石中磷的深層性質有利於在氫端具有輕摻雜的磷鑽石外延層中產生表面p 型導電性。因此,可以實現基於輕摻雜n型鑽石平面製程的鑽石CMOS。透過使用MEMS技術來設計能帶結構,n型鑽石MOSFET的性能可以進一步提高。這項研究揭示了單片整合鑽石晶片,其中電子學、自旋電子學和感測器都基於鑽石。

結論

總之,在磷摻雜同質外延(111) 鑽石外延層上展示了n 型通道鑽石MOSFET。 n型(111)鑽石外延層是基於步進流成核模式( step-flow nucleation mode)生長的,能夠精確控制晶體質量和施主分佈。 n-MOSFET 在573 K 時表現出約150 cm 2 V -1 s -1的高遷移率,這是高溫下優於其他寬帶隙半導體的顯著特徵。優異的高溫性能為開發用於惡劣環境下的高功率電子裝置、整合自旋電子學和極端感測器的鑽石CMOS 電路提供了途徑。(半導體產業觀察)